Tsinghua University, Beijing, China (1), CSR Zhuzhou Institude CO., LTD, Zhuzhou, China (2)

# DC-Link Voltage Balancing Method with Reduced Common-Mode Voltage for a Five-Level ANPC Inverter

**Abstract**. This paper presents a DC-link voltage balancing method with reduced common-mode voltage for a five-level active neutral-point clamped (ANPC) inverter. The DC-link voltage balancing method is based on zero-sequence voltage injection using carrier-based PWM. By further limiting the range of injected zero-sequence voltages, the amplitude of common-mode voltage can be reduced to 1/4 of the dc-link voltage. Experimental results are presented to verify the validity of this method.

Streszczenie. W artykule przedstawiono metodę balansowania napięciami kondensatorów obwodu pośredniczącego DC dla pięcio-poziomowego falownika Active NPC z redukcją napięcia common-mode. W metodzie wykorzystywana jest modulacja PWM z falą nośną i sygnałem kolejności zerowej, o regulowanym zakresie aplikacji. Przedstawiono wyniki eksperymentalne. (Wyrównywanie napięć w DC-link w pięciopoziomowym falowniku ANPC – redukcja napięcia common-mode).

**Keywords:** DC-link voltage balancing, common-mode voltage, zero-sequence voltage, five-level ANPC converter. **Słowa kluczowe:** balansowanie napięciami DC-link, napięcie common-mode, napięcie kolejności zerowej, pięcio-poziomowy przekształtnik ANPC.

## Introduction

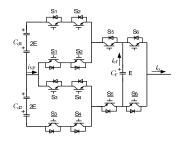

Multilevel converters receive increasing attentions in recent years due to the requirement of high power and high voltage in power industrial applications [1-3]. Plenty of multilevel topologies have been investigated, but only several of them are practical for industrial applications [1]. Among the existing multilevel converters, neutral-point clamped (NPC) and cascaded H-bridge multilevel converters are the most widely used [2]. As a completely mature topology, three-level NPC converter has become the industry standard in medium-voltage (2.3, 3.3 and 4.16 kV) applications [3]. However, limited by the present semiconductor blocking voltage ratings, three-level NPC converter is hard to be applied to high voltage drives over 6 kV. Although five-level NPC converter is a choice in this case, it suffers from the voltage imbalance of dc-link capacitors and requires mass clamping diodes [3]. Flyingcapacitor (FC) converter is another multilevel topology suitable for high power applications [4]. By properly using the redundant switching states, the voltages across all floating capacitors can be balanced. But it also requires mass clamping capacitors as the voltage level increases, which increases the cost and control complexity and makes the topology not so competitive for high voltage applications [2]. Five-level active neutral-point clamped (5L-ANPC) converter first proposed in 2005 [5] is an excellent multilevel topology which can overcome the above mentioned drawbacks in the NPC and FC multilevel converters [5] without transformers. A single phase of the 5L-ANPC converter is shown in Fig. 1. This paper proposes a DC-link voltage balancing method by zero-sequence voltage injection which can also reduce the common-mode voltage. Experimental results are presented to verify this method.

Fig.1. One phase leg of the 5L-ANPC inverter.

## **Neutral-Point Current Calculation**

As shown in Fig. 1, the phase leg of the 5L-ANPC converter is comprised of twelve equally rated devices and a floating capacitor  $C_{\rm f}$ .

Assume the dc-link voltage is 4E and the floating capacitor voltage is E. According to the above operating rules, each phase leg can output five voltage levels with eight distinct switching states. Defining the floating capacitor current is  $i_{cf}$  and neutral point (NP) current is  $i_{NP}$ , all the switching states with corresponding  $i_{cf}$  and  $i_{NP}$  are list in Table 1.

| Table 1. Switc | hing states c | of the 5L-AN | PC inverter |

|----------------|---------------|--------------|-------------|

|----------------|---------------|--------------|-------------|

| S1 | S2 | S3 | S4 | S5 | <b>S</b> 6 | $V_{o}$ | $i_{\rm cf}$            | i <sub>NP</sub> | Switching<br>states |

|----|----|----|----|----|------------|---------|-------------------------|-----------------|---------------------|

| 0  | 0  | 0  | 0  | 0  | 0          | -2E     | 0                       | 0               | V0                  |

| 0  | 0  | 0  | 0  | 0  | 1          | -E      | i,                      | 0               | V1                  |

| 0  | 0  | 0  | 0  | 1  | 0          | -E      | - <i>i</i> <sub>o</sub> | i,              | V2                  |

| 0  | 0  | 0  | 0  | 1  | 1          | 0       | 0                       | i,              | V3                  |

| 1  | 1  | 1  | 1  | 0  | 0          | 0       | 0                       | i,              | V4                  |

| 1  | 1  | 1  | 1  | 0  | 1          | Е       | i <sub>o</sub>          | i,              | V5                  |

| 1  | 1  | 1  | 1  | 1  | 0          | Е       | $-\dot{i}_{o}$          | 0               | V6                  |

| 1  | 1  | 1  | 1  | 1  | 1          | 2E      | 0                       | 0               | V7                  |

As shown in Table 1, for voltage levels -E, 0 and E, each corresponds to two redundant switching states. The floating capacitor current  $i_{cf}$  is related with -E and E.

For voltage level -E, states V1 and V2 generate the same voltage level with reverse  $i_{cf}$ . When the phase current  $i_o$  is positive, the state V1 will discharge the floating capacitor while state V2 will charge it. It is the same for voltage level *E* with states V5 and V6. So the floating capacitor voltage can be controlled by selecting different redundant switching states.

For a reference phase voltage  $u_x$  (-2  $\leq u_x \leq$  2), x represents the phase a, b or c, the duty cycle of outputting voltage level k (k = -2, -1, 0, 1 or 2) is defined as follows:

(1)

$$d_x^k = \begin{cases} u_x - k + 1, & u_x \in [k - 1, k) \\ k + 1 - u_x, & u_x \in [k, k + 1) \end{cases}$$

As can be seen from Table I, the two redundant switching states of both voltage levels -E and E have different effects on the NP current. So the average NP current of a single phase in a switching period can be

calculated depending on the duty cycle of voltage level k and the redundant switching state it used.

If V1 is used to generate voltage level -E, then the average NP current in a switching period can be written as follows:

(2)

$$\bar{i}_{NPx} = \begin{cases} 0, & u_x \in [-2, -1) \\ d_x^0 \cdot i_x, & u_x \in [-1, 0) \end{cases}$$

If V2 is used to generate voltage level -E, then the average NP current in a switching period is:

(3)

$$\bar{i}_{NPx} = \begin{cases} d_x^{-1} \cdot i_x, & u_x \in [-2, -1] \\ d_x^{-1} \cdot i_x + d_x^0 \cdot i_x, & u_x \in [-1, 0] \end{cases}$$

If V5 is used to generate voltage level *E*, then the average NP current in a switching period is:

(4)

$$\bar{i}_{NPx} = \begin{cases} d_x^0 \cdot i_x + d_x^{+1} \cdot i_x, & u_x \in [0,1) \\ d_x^{+1} \cdot i_x, & u_x \in [1,2] \end{cases}$$

If V6 is used to generate voltage level *E*, then the average NP current in a switching period is:

(5)

$$\bar{i}_{NPx} = \begin{cases} d_x^0 \cdot i_x, & u_x \in [0,1) \\ 0, & u_x \in [1,2] \end{cases}$$

Based on equations (1) - (5), the average NP current in a switching period generated by reference voltage  $u_x$  can be calculated. In a three-phase system, the average NP current in a switching period can be obtained:

(6)

$$\overline{i}_{NP} = \overline{i}_{NPa} + \overline{i}_{NPb} + \overline{i}_{NPc}$$

In order to maintain the DC-link capacitor voltages balanced and eliminate the offset, a reference NP current is expected to inject into the neutral point. Assuming the DClink voltage deviation is

$$\Delta u = u_{\rm d1} - u_{\rm d2}$$

where:  $u_{d1}$  and  $u_{d2}$  – voltages of the upper and lower dc-link capacitors. the demanded NP current can be written as:

(8)

$$i_{\rm NP,ref} = -C \frac{\Delta u}{t_{\rm p}}$$

where: C – capacitance value of  $C_{d1}$  and  $C_{d2}$ ,  $t_p$  – switching period. The target of DC-link voltage balancing method is to generate the demanded NP current by injecting a proper zero-sequence voltage.

Fig. 2. Diagram of zero-sequence voltage injection.

#### **Zero-Sequence Voltage Injection**

As the only freedom degree in carrier-based PWM, zero-sequence voltage does not affect the output line

voltage and current, but different zero-sequence voltages can lead to different switching states and so generate different NP currents.

#### **Common-Mode Voltage Reduction**

(

For a three-phase inverter, common-mode voltage is defined as:

9)

$$U_{\rm CM} = (U_{\rm ao} + U_{\rm bo} + U_{\rm co})/3$$

where:  $U_{\rm CM}$  – the common-mode voltage,  $U_{\rm ao}$ ,  $U_{\rm bo}$  and  $U_{\rm co}$  – the actual instantaneous values of output three-phase voltages, which are -2E, -E, 0, *E* or 2E.

The three-phase reference voltages can be written as the sum of a integer and a positive decimal:

(10)

$$\begin{cases} u_{a} = [u_{a}] + \{u_{a}\} \\ u_{b} = [u_{b}] + \{u_{b}\} \\ u_{c} = [u_{c}] + \{u_{c}\} \end{cases}$$

where:  $u_a$ ,  $u_b$  and  $u_c$  – three-phase reference voltages before injecting zero-sequence voltage,  $[u_a]$ ,  $[u_b]$  and  $[u_c]$  – rounded down integer parts of  $u_a$ ,  $u_b$  and  $u_c$ ,  $\{u_a\}$ ,  $\{u_b\}$  and  $\{u_c\}$  – positive decimal parts of  $u_a$ ,  $u_b$  and  $u_c$ .

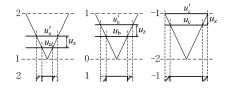

For carrier-based PWM, the output phase voltage only changes between two adjacent voltage levels in a switching period, so the instantaneous value of phase voltage can only be  $[u_x]E$  or  $([u_x]+1)E$ . The common-mode voltage in a switching period is described in Fig. 3. It has four values:  $\frac{[u_a]+[u_b]+[u_c]}{3}E$ ,  $\frac{[u_a]+[u_b]+[u_c]+1}{3}E$ ,  $\frac{[u_a]+[u_b]+[u_c]+2}{3}E$  and  $\frac{[u_a]+[u_b]+[u_c]+3}{3}E$ . Owing to  $u_a + u_b + u_c = 0$ , then

$\{u_a\}+\{u_b\}+\{u_c\}$  can be 1 or 2 and so  $[u_a]+[u_b]+[u_c]$  can be -1 or -2. All the possible common-mode voltages are summarized in Table 2.

Fig. 3 Generation of common-mode voltage

After injecting zero-sequence voltage, the situation is more complex, because the sum of  $u'_a$ ,  $u'_b$  and  $u'_c$  is no more zero, hence the sum of  $[u'_a]$ ,  $[u'_b]$  and  $[u'_c]$  has many possible values. Since  $-2 \le u'_x \le 2$ , the minimal value of  $[u'_a] + [u'_b] + [u'_c]$  can reach -6 and the maximal value can reach 4. When applying the proposed zero-sequence voltage injection method, one of the three reference phase voltages is an integer, so the common-mode voltage in a switching period has three values. All the possible common-mode voltages are summarized in Table 3.

Table 2. Possible common-mode voltages without zero-sequence voltage injection

| $[u_{\rm a}] + [u_{\rm b}] + [u_{\rm c}]$ | Common-mode voltages                          |

|-------------------------------------------|-----------------------------------------------|

| -1                                        | -E/3, 0, E/3, 2E/3                            |

| -2                                        | -2 <i>E</i> /3, - <i>E</i> /3, 0, <i>E</i> /3 |

Form table 2 and table 3 it can be seen that the amplitude of common-mode voltage without zero-sequence voltage injection is 2E/3 and is increased to 2E after zero-sequence voltage injection. In order to limit the amplitude of

the common-mode voltage, the range of injected zerosequence voltage must be limited. However, too narrow range of zero-sequence voltage will also make the DC-link volatge balancing effect poor.

Table 3. Possible common-mode voltages after zero-sequence voltage injection

| $[u'_{a}] + [u'_{b}] + [u'_{c}]$ | Common-mode voltages                       |

|----------------------------------|--------------------------------------------|

| -6                               | -2E, $-5E/3$ , $-4E/3$ ,                   |

| -5                               | -5E/3, $-4E/3$ , $-E$                      |

| -4                               | -4E/3, $-E$ , $-2E/3$                      |

| -3                               | - <i>E</i> , -2 <i>E</i> /3, - <i>E</i> /3 |

| -2                               | -2E/3, $-E/3$ , 0                          |

| -1                               | -E/3, 0, E/3                               |

| 0                                | 0, <i>E</i> /3, 2 <i>E</i> /3              |

| 1                                | E/3, 2E/3, E                               |

| 2                                | 2E/3, E, 4E/3                              |

| 3                                | E, 4E/3, 5E/3                              |

| 4                                | 4 <i>E</i> /3, 5 <i>E</i> /3, 2 <i>E</i>   |

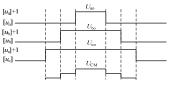

# (11) $-3 \le [u'_{a}] + [u'_{b}] + [u'_{c}] \le 1$

### **Experimental Results**

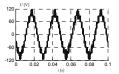

A low power three-phase 5L-ANPC inverter prototype has been built up to verify the proposed control method. Infineon IGBT module BSM75GB120DN2 is used as the power semiconductor switch. The DC-link capacitor is 500  $\mu$ F and the floating capacitor is 1 mF. The switching frequency is 2 kHz and the DC-link voltage is set at 120V.

Fig. 4 shows the output phase current and phase to phase voltage and Fig. 5 depicts the voltages of floating capacitors. It can be seen that all the three-phase floating capacitors are regulated at their reference voltage and the ripple amplitude is limited within 2 V.

Fig. 4. Phase current and phase to phase voltage

Fig. 5. Three-phase floating capacitor voltages

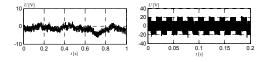

Fig. 6. NP potential and common-mode voltage without zero-sequence voltage injection  $% \left( {{\left[ {{{\rm{T}}_{\rm{T}}} \right]}_{\rm{T}}} \right)$

Fig. 6 is the experimental results of NP potential  $U_{\rm NP}$  and common-mode voltage  $U_{\rm CM}$  when the DC-link voltage

balancing method is not used. When the DC-link voltage balancing method is utilized, the experimental results are shown in Fig. 7 and Fig. 8. Fig. 7 is the experimental result when the range of zero-sequence voltage is not limited.

Fig. 7. NP potential and common-mode voltage with unlimited zerosequence voltage injection

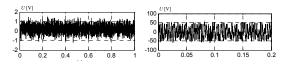

Fig. 8. NP potential and common-mode voltage with proposed DClink voltage balancing method

When limiting the range of injected zero-sequence voltage with formula (11), the experimental results is shown in Fig. 8. The offset in the NP potential is also eliminated completely and the voltage ripple is slightly inceased to 2 V. But the common-mode voltage is reduced to 30 V.

# Conclusions

This paper has presented a DC-link voltage balancing method based on zero-sequence voltage injection. By selecting some key zero-sequence voltages and calculating their corresponding average NP currents, the most appropriate zero-sequence voltage can be selected to generate the demanded NP current. By limiting the range of the injected key zero-sequence voltage, the common-mode voltage is reduced to 1/4 of the DC-link voltage. Experimental results demonstrat the validity of this method.

#### REFERENCES

- [1] S. Kouro, M. Malinowski, K. Gopakumar, J. pou, L. G. Franquelo, B.Wu, J. Rodriguez, M. A. Perez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters," IEEE Transactions on Industrial Electronics, vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

- [2] J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro, "Multilevel voltage-source-converter topologies for industrial medium-voltage drives," IEEE Trans. Ind. Electron., vol. 54, no. 6, pp. 2930–2945, Dec. 2007.

- [3] J. Rodriguez, S. Bernet, P. K. Steimer and I. E. Lizama, "A Survey on Neutral-Point-Clamped Inverters," IEEE Transactions on Industrial Electronics, vol. 57, no. 7, pp. 2219 -2230, 2010.

- [4] T. A. Meynard and H. Foch, "Multilevel conversion: High voltage choppers and voltage source inverters," in Proc. of IEEE Power Electronics Specialists Conference (PESC), pp. 397-403, 1992.

- [5] P.Barbosa, P.Steimer, J.Steinke, L.Meysenc, M.Winkelnkemper and N.Celanovic, "Active neutral-pointclamped (ANPC) multilevel converter technology," in Proc. of European Conference on Power Electronics and Applications (EPE), pp. 1-10, 2005.

Authors: dr. Kui Wang, Tsinghua University, Beijing 100084, China, E-mail: <u>wangkui@tsinghua.edu.cn</u>; prof. Yongdong Li, Tsinghua University, Beijing 100084, China, E-mail: <u>liyd@tsinghua.edu.cn</u>; dr. Zedong Zheng, Tsinghua University, Beijing 100084, China, Email: <u>zzd@tsinghua.edu.cn</u>; dr. Lie Xu, Tsinghua University, Beijing 100084, China, E-mail: <u>xulie@tsinghua.edu.cn</u>; prof. Jianghua Feng, CSR Zhuzhou Institude CO., LTD, Zhuzhou 412001, China, E-mail: <u>fengih@teg.cn</u>;