## Andrzej KASPRZAK<sup>1</sup>, Marek ORLIKOWSKI<sup>1</sup>, Dariusz BRODECKI<sup>1</sup>, Mariusz KULAWIŃSKI<sup>2</sup>

Politechnika Łódzka, Instytut Elektroenergetyki - Zakład Przekładników i Kompatybilności Elektromagnetycznej (1) "SARA WERNAU" sp. z o.o. (2)

# About Advantages of EMC Development Testing on Example of Function Generator

Abstract. In the paper, the solution of EMC problem concerning excessive levels of conductive and radiated emissions in the construction of function generator has been presented. The EMC troubleshooting that has been described illustrates advantages of pre-compliance diagnostic testing to modify device construction at early stages of development.

Streszczenie. W artykule przedstawiono rozwiązanie problemu EMC dotyczącego nadmiernych poziomów emisji przewodzonych i emisji promieniowanych w konstrukcji generatora funkcyjnego. Opisane zagadnienie obrazuje zalety stosowania badań diagnostycznych typu "precompliance" do modyfikacji urządzenia we wczesnych fazach rozwoju konstrukcji (O zaletach badań konstruktorskich EMC na przykładzie generatora funkcyjnego).

Keywords: EMC diagnostic testing, EMC development testing, function generator. Słowa kluczowe: badania diagnostyczne EMC, badania konstruktorskie EMC, generator funkcyjny.

#### Introduction

Practically, all everyday usage electrical and electronic equipment produce unintentional (it means unexpectedly) electromagnetic disturbances of RF energy. Such disturbances can transfer in conducted way (e.g. through mains) or in radiated way (through air) and can cause interferences to other electrical devices of insufficient level of immunity [1].

Control of electromagnetic compatibility (EMC), what means control of emission level and immunity level is an increasing necessity. In order to limit emissions and improve immunity of products engineers should apply correct design methods what ensures not only reliable operation, reduces project time and money but they should also apply "EMC in mind" - how to meet EMC regulatory requirements [2]. Design analysis from EMC point of view and some tests should be performed at all stages of product development [3][4]. This enables to bring in a product necessary modifications during the preliminary design cycle.

Early phases of product development enable to apply simple and relatively cheap methods to ensure compliance – known as "pre-compliance" testing. This kind of testing does not involve expensive instrumentation and does not require specific measurement procedures in detail defined in EMC standards while keeping "full compliance" testing. Standard test methods (full compliance) do not identify where the emissions are coming from, only that they exist. Therefore, it is good to apply various "pre-compliance" diagnostic techniques which usually let to localize EMC problem. Such development testing has the advantage that tests can be stopped at any time, the EUT modified, and the test redone.

Common "pre-compliance" diagnostic devices among others are:

- oscilloscopes,

- spectrum analyzers,

- simple dipole antennas,

- close-field probes,

besides, such input interfaces as simple dipole antennas or close-field probes are easy to be home-made.

EMC Lab of Politechnika Lodzka supports local manufacturers enabling them performing tests throughout all stages of product's development cycle. This paper describes an example of such development testing which illustrates how the design of function generator was being modified. It will be demonstrated that in devices with digital processing is possible up to 40dB reducing of emissions after applying some measures especially with regard to clocking frequency and right choice of elements of circuit.

#### Description of equipment under test (EUT)

Function generator (EUT) has been structured on the basis of specialized IC component. Generator can be tuned from 1Hz up to 200kHz within five ranges. Digital circuitry of the generator is composed of two common 8-bit processors which are timed by the 20MHz clock (in the primary version). Application of two processors made the question of programming much simpler. One processor runs buttons, LED display and relays changing ranges and function of the generator. Second processor is only dedicated for measuring a frequency of the waveform that is currently generated. Results of periodically performed measurements are sent to main processor which runs all other functions of the generator.

Whole circuitry is powered from classic transformer supply which delivers stabilized voltages +9V, –9V, +5V.

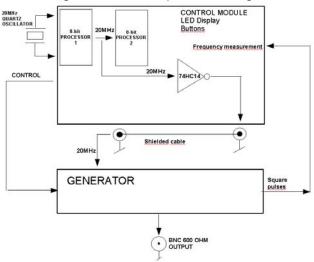

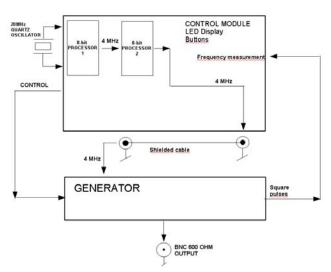

Block diagram of the EUT is presented in Figure 1.

Fig.1. Diagram of the EUT in a primary version

#### Primary version of EUT development testing

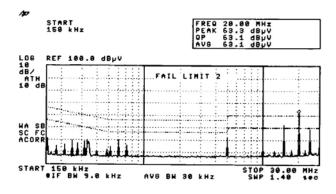

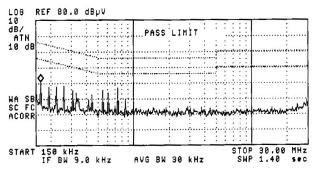

Testing for conducted emission [5][6] in the range 150kHz - 30MHz has failed (Figure 2).

Fig.2. Results of conducted emission measurement of the EUT in a primary version (PEAK detector)

It should be noticed that the highest emission appears with the 20MHz frequency (timing clock frequency) and significantly exceeds QP and AVG limits.

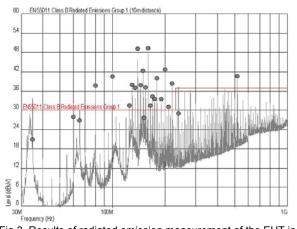

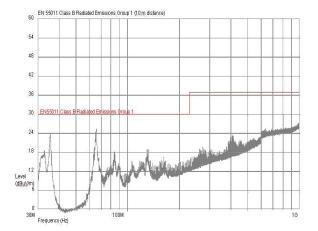

Testing for radiated emission in the range 30MHz -1GHz has demonstrated contribution of higher harmonics coming from 20MHz clock signal - visibly exceeding limits (Figure 3).

Fig.3. Results of radiated emission measurement of the EUT in a primary version (PEAK detector)

Such negative results of testing for conducted and radiated emission of EUT primary version made the manufacturer to analyze the design once more.

#### EMC analysis and modifications performed

In most of electronic devices the reason of occurring excessive levels of emission are the sharp slopes of pulses created by digital circuitry.

As a result of analysis it has been proposed to modify the design by removing 74HC14 Schmitt Trigger gate from the line: 20MHz quartz oscillator – generator.

Schmitt Trigger gate buffers clock signal of the processor in order to separate the clock from the load coming from generator and capacitances of shielded cable which connects clock to generator. In the first stage of modification (after removing the Schmitt Trigger gate) clock signal needed for generator has been brought from a clock output of the auxiliary processor, that was still timed by 20MHz pulses created in the main processor.

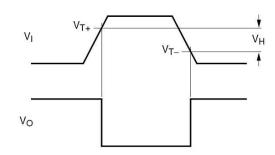

The decrease of emission level has been observed for the frequencies being harmonic components of 20MHz signal. It results from lower speed of rising/falling the slopes of clocking signal brought from a processor output in contrary to the signal generated by the 74HC14 Schmitt Trigger gate output (Figure 4).

Fig.4. Input signal  $V_1$  and output signal  $V_0$  of Schmitt Trigger gate

Since the decrease of emission level was evident but it still could not give any guaranties to meet the regulatory requirements, so the another modification of the device has been done. The clock frequency has been lowered by replacing 20MHz quartz oscillator with 4MHz one. This change forced modification of programming codes of both processors in order to adapt the programme to a new clocking frequency of processors. The change of timing frequency from 20MHz to 4MHz has lowered the level of emission radically.

Block diagram of the EUT after modifications is presented in Figure 5.

Fig.5. EUT block diagram after modifications

#### Final version of EUT development testing

Conducted emission measurement in the frequency range 150kHz - 30MHz illustrates Figure 6.

Fig.6. Results of conducted emission measurement of the EUT after modifications (PEAK detector)

Radiated emission measurement in the frequency range 30MHz – 1GHz presents Figure 7.

Fig.7. Results of radiated emission measurement of the EUT after modifications (PEAK detector)

The function generator (EUT) which was tested meets the EMC regulatory requirements with regard to conducted and radiated emissions what shows that modifications performed were fully reasonable.

### Conclusions

• If the requirements related to functioning of the digital device do not force specific value of timing frequency, then one should avoid high frequencies of clocking.

• Other elements of the digital device that can cause high levels of emissions are logic gates creating very sharp slopes of pulses (e.g. Schmitt Trigger gates).

• The experiments demonstrated that in conditions outside EMC laboratory (at manufacturer or designer) is quite easy to assess modifications performed - by the observation of emissions generated from the device having

only common spectrum analyzer and simple dipole antenna.

#### REFERENCES

[1] Markowska R., Sowa A., Wiater J. Symulacyjne badania zagrożeń piorunowych systemów elektronicznych - Przegląd Elektrotechniczny 2010/3

[2] Guide for the EMC Directive 2004/108/EC

(8th February 2010) http://ec.europa.eu/enterprise/sectors/electrical/files/emc\_guide\_u pdated\_20100208\_v3\_en.pdf

[3] Maintaining EMC in Production, M Fitzpatrick, EMC 92 -Designing EMC into your Product, Conference Proceedings, ERA Report 92-0011, February 1992

[4] Maddocks A J, Testing During Development, EMC 93 -Achieving Whole-Life EMC: Management, Design and Compliance, Conference Proceedings, ERA Report 93-0013, February 1993

[5] PN-EN 61326-1:2009 - Wyposażenie elektryczne do pomiarów, sterowania i użytku w laboratoriach Wymagania dotyczące kompatybilności elektromagnetycznej (EMC)

[6] PN-EN 55011:2007 - Przemysłowe, naukowe i medyczne urządzenia o częstotliwości radiowej -- Charakterystyki zaburzeń elektromagnetycznych -- Dopuszczalne poziomy i metody pomiarów

dr inż. Dariusz Brodecki, Politechnika Łódzka, Katedra Elektrotechniki Ogólnej i Przekładników, ul. Stefanowskiego 18/22, 90-924 Łódź, E-mail: <u>darekb@p.lodz.pl;</u>

mgr inż. Mariusz Kulawiński, SARA WERNAU sp.z o.o., ul. Milionowa 21, 93-105 Łódź, E-mail: <u>mariusz@bgs.pl;</u>

The correspondence address is: e-mail: andkaspr@p.lodz.pl

**Authors**: dr inż. Andrzej Kasprzak, Politechnika Łódzka, Katedra Elektrotechniki Ogólnej i Przekładników, ul. Stefanowskiego 18/22, 90-924 Łódź, E-mail: <u>andkaspr@p.lodz.pl</u>;

dr inż. Marek Orlikowski, Politechnika Łódzka, Katedra Elektrotechniki Ogólnej i Przekładników, ul. Stefanowskiego 18/22, 90-924 Łódź, E-mail: <u>marekorl@p.lodz.pl</u>;